# Digitalno načrtovanje

Izvajalca: prof. dr. Patricio Bulić in doc. dr. Nejc Ilc Asistent: Ratko Pilipović

#### **Proces**

777

<ime\_procesa>: process (<sensitivity\_list>)

begin

--koda procesa

end

v <sensitivity\_list> navedemo vse signale, ki bodo povzročili spremembe na izhodih iz procesa

### if stavek

• Uporaben samo znotraj procesa 👡 🗲 🥂

```

if pogoj then

--prireditve

else

--prireditve

end if;

if pogoj then

--prireditve

elsif pogoj then

--prireditve

else

--prireditve

else

--prireditve

end if;

```

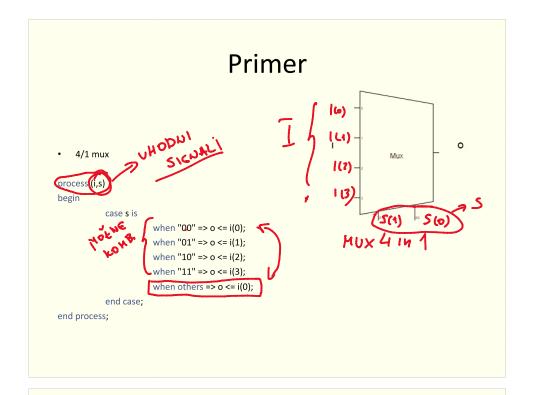

#### case stavek

```

case(s) is

when vred1 => izhod <= izraz1;

when vred2 => izhod <= izraz2;

when vred3 => izhod <= izraz3;

when others => izhod <= izraz4;

end case;</pre>

```

• zadnji (default) člen je obvezen

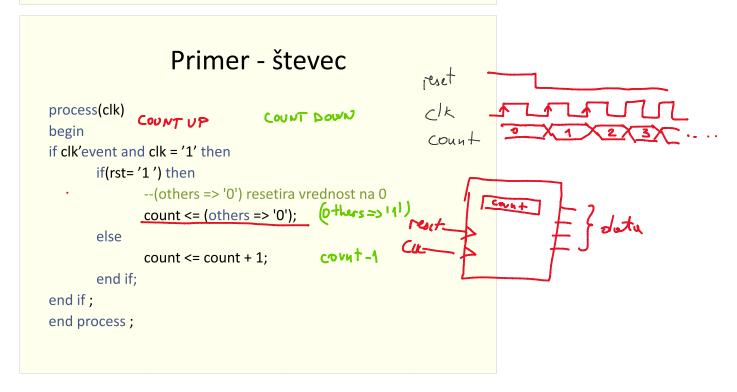

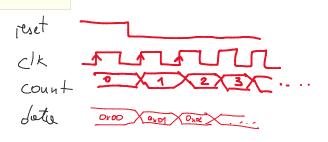

# Sekvenčna vezja

V sekvenčnih vezjih se spremembe dogajajo ob dogodkih ure (prvi/zadnji fronti)

• Dogodek na signalu ure zaznamo z clk'event

- clk je signal za uro

- 'event je true, ko je prišlo do spremembe signala

- Prva fronta clk'event and clk = '1'

- Zadnja fronta clk'event and clk = '0'

clki event ond clk=111

# Primer – D celica CLK ENOTEND. SENS. CUST process(clk) begin if clk'event and clk = '1' then q <= d; end if; end process;

## VHDL knjižnice

• Če ste bili pozorni ste v VHDL kodi opazili:

```

library IEEE; use IEEE. STD_LOGIC_1164. ALL;

```

- knjižnica IEEE. STD\_LOGIC\_1164 definira tipa STD\_LOGIC in STD\_LOGIC\_VECTOR ter nekaj uporabnih funkcij, naprimer:

- rising edge (namesto clk'event and clk = '1')

- falling\_edge (namesto clk'event and clk = '0')

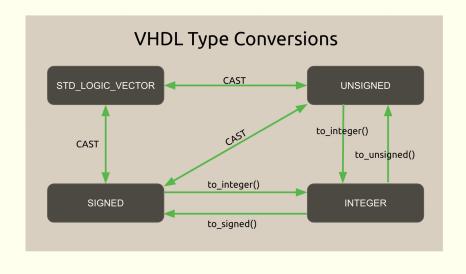

#### IEEE.NUMERIC\_STD

use IEEE.NUMERIC\_STD.ALL

- Definira <u>aritmetične operacije in tipove unsigned</u> in signed!!!

- definira naslednje operacije nad unsigned in signed!!!!:

### IEEE.NUMERIC\_STD

#### use IEEE.NUMERIC\_STD.ALL

- Pri uporabi aritmetičnih operacij rezultat ali operande kastovati v/iz signed ali unsigned tipa

- F-je za kastovanje

- (un)signed(ime\_vektora)

- std\_logic\_vector(ime\_vektora)

- to\_integer(), to\_signed(), to\_unsigned()

# Konverzija tipov

# Naloga

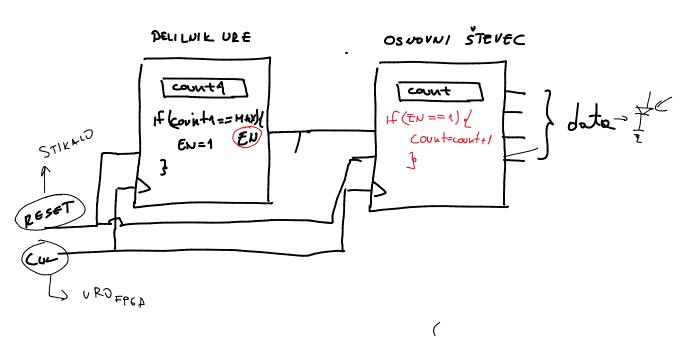

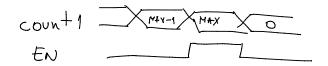

Napišite VHDL modul, ki bo ustvaril vzorec "pomikanja" na LED (pol-sekundni interval)

$$\int = 100 MH_{2}$$

$$T = \frac{1}{100.106}$$